Recently, I have been teaching myself all about FPGAs. Well, truthfully, some about FPGAs. I have even been blogging about my learning experiences (see the Programmable Planet links to the left). I am using an Opal Kelly XEM3005 board as my learning tool. I bought this board several years ago, and only just got arouund to trying to figure this stuff out...

I am using Xilinx ISE WebPack environment (because it's Windows based and free!). I started out using the schematic capture tools, since schematics are what I am most familiar with. After a while, though, I moved on to a Hardware Description Language (HDL). In particular, the language that I am teaching myself is called "Verilog"

As apart of my self-teachings, I decided that a nifty (and easy to test) project to pursue would be a logic analyzer. And so here we are. This package uses National Instruments LabWindows/CVI as the software development environment. The project can be internally or externally triggered, sampling rates can be set across a multitude of values, and up to 16 million samples can be captured at a time. All waveforms are displayed on the screen, and can be scrolled and zoomed.

An installer, as well as all source code and projects are available for download at the end of this page.

So, how does this thing work? First, you've got to have an Opal Kelly XEM3005 board - it won't work with anything else. Also, you need the BRK3005 breakout board, unless you're willing to make your own... Make sure all the drivers are installed according to the instructions that come with the device.

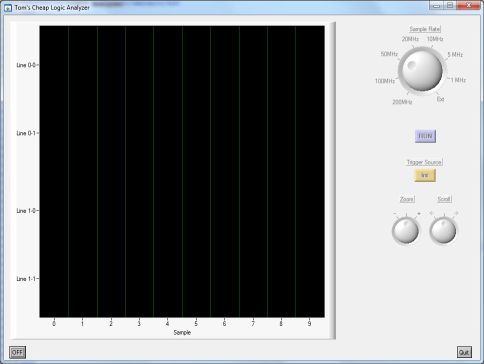

Next, you need to download the GUI installer (WARNING!! It's 180MB!). Extract the contents of this zip file to some temporary location, and run the installer (setup.exe. Once the GUI is installed, there should be a new folder under Start->All Programs that is called LogicAnalyzer. Execute the program that resides in that folder, and you should see the following:

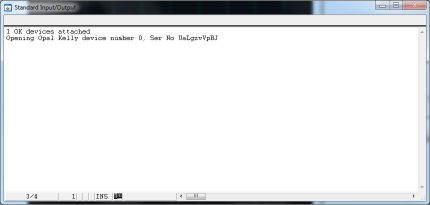

Ensure that the Opal Kelly board is connected tot he computer, and click the "OFF" button in the lower left corner of the GUI. This will connect the software to the Opal Kelly board, and "bang" the bitfile to the board. If all goes well, you should see the following:

Now the analyzer is up and running! Data inputs are on the following pins of the breakout board:

in addition to those 16 data inputs, there is an input for an external clock which can be used to set the sampling rate:

There is a single output from the hardware, and that is the selected sample clock. You can use this to synchronize the unit under test to the logic analyzer:

Once everything is up and running, the logic analyzer is ready for use. Note that the inputs are not buffered, and 3.3V inputs are expected. Sample rate is selected using the "knob" on the upper right side of the GUI. Choices are:

If the trigger source is set to "Ext" (by clicking that button), the logic analyzer will be "armed," and will not begin sampling data until the logic level on DataIn<15> transitions from low to high, allowing captures to be synchronized with that input.

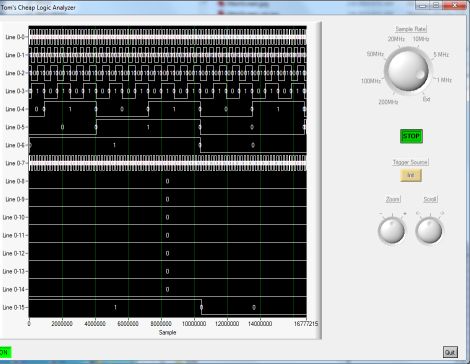

Once triggered (either externally or internally, the RUN button becomes a green "STOP" button as shown below. This button may be clicked at any time to abort the acquisition.

Once a trigger is received, the logic analyzer acquires 16,000,000 samples (32MB), and stores them into on-board memory. The data is then transferred to the PC and displayed on the GUI. To the right of the display, there are two knobs that allow control of zoom and scroll. Scrolling is not available unless the data has some level of zoom applied.

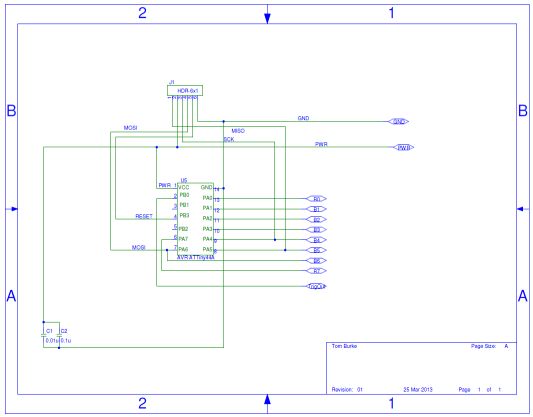

For testing this thing, I used an Atmel ATTiny microcontroller on an old solderless breadboard. The schematic of this is below, and all the source code is available in the downloads.

That's it. If you find it useful, awesome. If not... Well, what do you expect for free?

The links below are the downloads that I've made available: